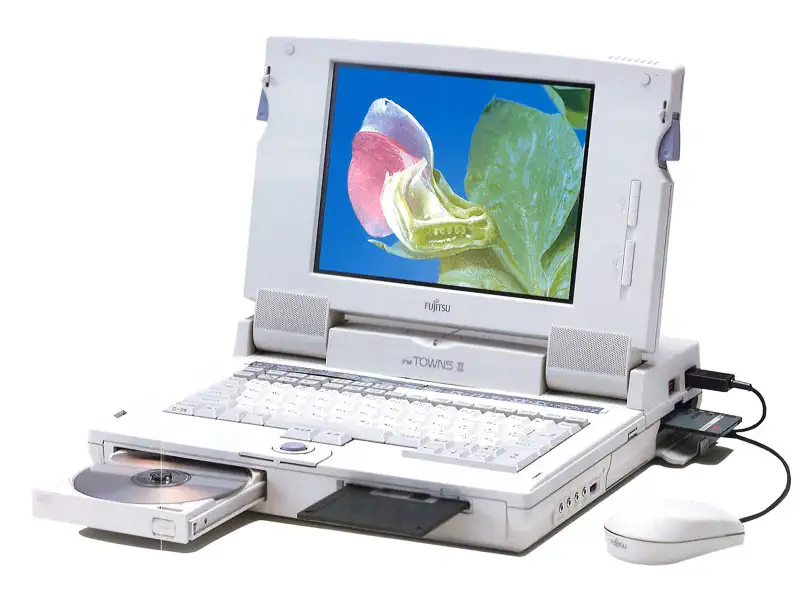

Fuji FM-Towns 2

The FM Towns II computer came in a few configurations, displayed here is the FM Towns II Laptop, which had a built in CD-ROM, a 3.5" disk drive and all the specifications of the FM Towns computer, but now ran on the Intel 80486DX2 CPU @ 66MHz.

A desktop version of the FM-Towns II with separate screen also exists.

The FM-Towns Architecture was, like the Sharp X68000 series, serious about graphics. The system had hardware sprites, and could display up to 1024 sprites on screen simultaneously, each sprite being 16x16 in 16 colors. There was 128KByte of memory reserved for sprites. Although advanced, the Sharp X68000 had even better sprite hardware for serious action gaming.

Towns OS

Towns OS was the system software environment designed for Fujitsu’s FM Towns computers, introduced in 1989. At its core, Towns OS was built on MS-DOS (specifically a customized variant), but with a tightly integrated graphical user interface layered over it. Unlike conventional DOS machines of the time, FM Towns booted directly from a CD-ROM–based operating system image into this GUI, bypassing the text-only DOS prompt. This made it one of the earliest consumer microcomputers to offer a graphical desktop environment as the default interface, rather than an optional shell.

Technically, Towns OS provided API-level extensions to leverage the FM Towns’ hardware features: its high-resolution graphics modes, 256-color palette from a 16.7 million color space, PCM audio, and CD-DA playback. Applications were written to access these resources directly through BIOS and Towns OS libraries, enabling multimedia-rich software. Because the underlying layer was DOS-compatible, developers could also use standard DOS file I/O and interrupt services, but Towns OS abstracted hardware-specific features to simplify multimedia development.

Over time, Towns OS evolved into a more sophisticated environment. Later versions adopted elements of Windows 3.x compatibility by running on top of DOS, allowing a subset of Windows applications to coexist with native Towns software. However, the system always retained its CD-ROM–centric architecture, with bootable CDs that carried both the OS kernel and applications. This design gave the FM Towns a hybrid identity: fundamentally a DOS machine, but one whose operating system was extended into a graphical, multimedia-oriented platform tightly coupled to its hardware.

Sound - Yamaha YM2612

The Yamaha YM2612 is a six-channel FM synthesis sound chip introduced in 1988, part of the OPN family derived from the YM2203. It implements a four-operator FM synthesis engine with 8 different operator algorithms, each defining how modulators and carriers are interconnected to generate complex harmonic spectra. Unlike earlier chips in the family, the YM2612 integrates both the synthesis core and a built-in 9-bit DAC (digital-to-analog converter), which simplified design for system integrators such as Sega in the Mega Drive/Genesis. The chip operates with a master clock typically at 7.67 MHz (in PAL/NTSC consoles) and divides this to produce the required timing for envelope generation, operator updates, and frequency modulation.

From a programming perspective, the YM2612 exposes a set of registers mapped through two I/O ports, typically interfaced via a Z80 or 68000 CPU. Each of the six channels can be individually programmed with parameters such as frequency number (10-bit F-NUM plus a 3-bit block for octave selection), operator detune values, multiple frequency multipliers, and envelope shaping controls (attack rate, decay rate, sustain level, release rate). Operators can be combined into algorithms to produce additive, subtractive, or complex FM timbres. The chip also supports low-frequency oscillation (LFO) modulation, applied globally, which can be used to add vibrato or tremolo to channels. The internal phase accumulators and envelope generators are updated at fixed sample intervals, and the internal synthesis resolution is higher than the external 9-bit DAC, meaning quantization artifacts are introduced at the analog output stage — one of the reasons the YM2612 has its characteristic “gritty” sound.

In addition to its six FM channels, the YM2612 provides a special channel 6 PCM mode, where the final channel can be switched from FM to direct 8-bit PCM sample playback. This mode bypasses the FM operators and routes CPU-fed data directly to the DAC, allowing sampled drums or sound effects to be played back in real time. Because the PCM data stream competes with the CPU and bus bandwidth, clever buffering and timing were required to maintain consistent sample rates. System programmers typically wrote to the YM2612 registers via tightly synchronized code or DMA, carefully balancing CPU usage with the chip’s strict write timing. This combination of six programmable FM channels plus one PCM channel made the YM2612 one of the most flexible and iconic synthesis chips of the late 1980s, enabling the distinctive sonic character of the Sega Mega Drive/Genesis.

Sound - Rico RF5C68 PCM

The Ricoh RF5C68 is an 8-channel PCM sound generator introduced in the late 1980s, used most notably in the Sega CD/Mega-CD as its dedicated sample playback processor. Architecturally, it is very different from FM chips like the YM2612: instead of operator-based synthesis, it implements a wavetable PCM playback engine, with each channel capable of independently fetching, looping, and mixing 8-bit samples stored in dedicated sound RAM. The chip supports up to 64 KB of external DRAM for waveform storage, which was large enough to hold multiple instrument or effect samples for use during gameplay or cutscenes. Each of the eight channels can operate at independently programmable sample rates, giving the system flexibility in layering percussion, melodic instruments, and sound effects.

From a programming perspective, the RF5C68 is controlled through a set of memory-mapped registers that define channel parameters such as sample start address, loop start address, and loop length, as well as per-channel volume and panning. Each channel has its own 12-bit frequency register, which sets the sample step rate, allowing for pitch shifting of the waveform. The playback engine supports auto-looping, meaning once a sample reaches its loop end address, it automatically restarts at the loop start, enabling sustained notes or repeating sound textures without continuous CPU intervention. Because all channels are mixed digitally inside the chip before conversion, programmers could assign precise balance and stereo placement, creating complex layered arrangements far beyond the capabilities of single-channel PSGs or beeper hardware.

The RF5C68 includes an internal 8-bit DAC for analog output, but unlike the YM2612, which was limited by its 9-bit DAC “ladder” noise, the Ricoh part offered cleaner playback suitable for digitized audio. In practice, developers combined its capabilities with CD-ROM streaming to play back higher fidelity voice samples, orchestral stings, or ambient effects alongside the YM2612’s FM synthesis. The chip required the programmer to carefully manage the waveform RAM contents, often uploading new samples on demand during gameplay, since 64 KB was modest for large sound libraries. This gave rise to hybrid techniques, where short percussive sounds were stored in RAM, while larger audio like voices or cutscene music streamed from CD. Overall, the RF5C68 complemented the FM-based YM2612 by providing a true multichannel PCM engine, enabling the Sega CD to achieve richer, more varied audio than cartridge-only systems of its era.

CPU - The Intel 80486

The Intel 80486 was introduced in 1989 as the successor to the 80386, marking the fourth generation of the x86 family. It integrated the features of the 386 with significant architectural enhancements, including an on-chip unified floating point unit in the DX models and an on-chip unified 8 KB L1 cache. This integration reduced the need for external coprocessors and external cache for basic workloads, which had been essential in the 386 era. The chip retained full backward compatibility with 16-bit real mode and 32-bit protected mode, ensuring that legacy software written for the 8086, 80286, and 80386 could execute unchanged.

The internal pipeline of the 80486 was redesigned to support five-stage instruction pipelining, which allowed it to complete most instructions in a single clock cycle under ideal conditions. This pipeline was composed of fetch, decode, execute, memory, and write-back stages, effectively doubling the performance per clock compared to the 386. Additionally, the instruction decoder was more sophisticated, capable of breaking down complex x86 instructions into simpler micro-operations that could be executed more efficiently. The presence of the integrated cache reduced memory latency, which was a significant bottleneck in earlier designs.

The 80486 family included multiple variants with different feature sets. The 80486DX incorporated both the FPU and L1 cache, while the 80486SX disabled the on-chip FPU, reducing cost for entry-level systems. The 80486DX2 and DX4 introduced clock multiplication, allowing the CPU core to run at 2x or 3x the external bus frequency. This meant that a system with a 33 MHz front-side bus could drive a DX2-66 running its core at 66 MHz. Intel also introduced the 80486 OverDrive processors, which were pin-compatible upgrades for existing 486 sockets, extending the usable life of installed systems by adding higher internal clock multipliers and sometimes cache enhancements.

Memory management in the 80486 remained based on the 80386 model, with full support for segmentation and paging. It implemented a 32-bit address bus, allowing access to 4 GB of physical memory, and a 32-bit data bus for efficient transfer of large operands. The paging unit supported 4 KB pages with full page-level protection, as well as demand-paged virtual memory when used with appropriate operating systems like Windows NT or Unix System V. Combined with the larger and faster cache, the 80486 could sustain much higher throughput in multitasking environments, making it the processor that bridged the transition from 16-bit DOS-centric computing to true 32-bit protected-mode operating systems.

RAM max: 36MB

8 channel 10-bit PCM

1 channel 16-bit 44.1kHz PCM